# SURENOO GRAPHIC OLED SERIES DISPLAY Product Specification

Part Name: OEL Display Module SOG25664C\_P280

Please click the following image to buy the sample

Shenzhen Surenoo Technology Co.,Ltd.

www.surenoo.com E-mail: info@surenoo.com

**Graphic OLED Display Selection Guide**

**Graphic OLED Module**

**Graphic OLED Panel**

SSD1322

www.surenoo.com - 01 -

# **Contents**

|           |      | ion History                                                     |             |

|-----------|------|-----------------------------------------------------------------|-------------|

|           |      | nts                                                             |             |

| 1.        | Bas  | sic Specifications                                              | 1~5         |

|           | 1.1  | Display Specifications                                          | 1           |

|           | 1.2  | Mechanical Specifications                                       | 1           |

|           | 1.3  | Active Area / Memory Mapping & Pixel Construction               | 1           |

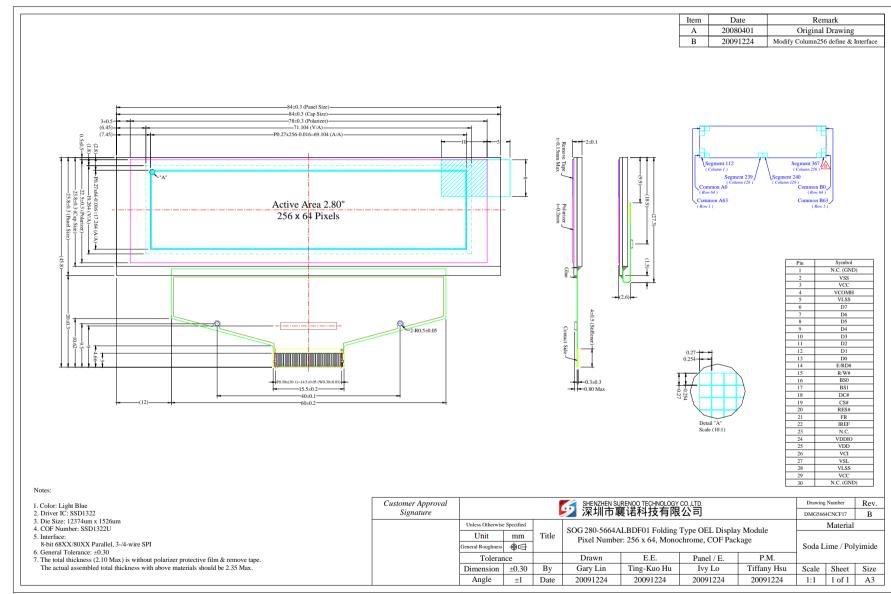

|           | 1.4  | Mechanical Drawing                                              | 2           |

|           | 1.5  | Pin Definition                                                  | 3           |

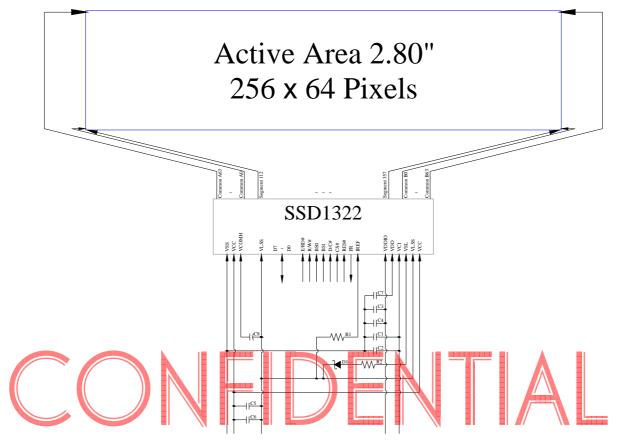

|           | 1.6  | Block Diagram                                                   | 5           |

|           |      | solute Maximum Ratings                                          |             |

| <i>3.</i> | Opt  | tics & Electrical Characteristics7                              | ~11         |

|           | 3.1  | Optics Characteristics                                          | 7           |

|           | 3.2  | DC Characteristics                                              | 7           |

|           | 3.3  | AC Characteristics                                              | 8           |

|           |      | 3.3.1 68XX-Series MPU Parallel Interface Timing Characteristics | 8           |

|           |      | 3.3.2 80XX-Series MPU Parallel Interface Timing Characteristics |             |

|           |      | 3.3.3 Serial Interface Timing Characteristics (4-wire Serial)   | 10          |

|           |      | 3.3.4 Serial Interface Timing Characteristics (3-wire Serial)   | 11          |

| 4.        | Fur  | Commands                                                        | ~14         |

|           | 4.1  | Commands                                                        | 12          |

|           | 4.2  | Power down and Power up Sequence                                | <b></b> 12  |

|           |      | 4.2.1 Power up Sequence                                         | 12          |

|           |      | 4.2.2 Power down Sequence                                       | 12          |

|           |      | Reset Circuit                                                   |             |

|           | 4.4  | Actual Application Example                                      | 13          |

| <i>5.</i> |      | liability                                                       |             |

|           | 5.1  | Contents of Reliability Tests                                   | 15          |

|           | 5.2  | Failure Check Standard                                          | 15          |

| 6.        |      | tgoing Quality Control Specifications16                         |             |

|           |      | Environment Required                                            |             |

|           | 6.2  | Sampling Plan                                                   | 16          |

|           | 6.3  | Criteria & Acceptable Quality Level                             | 16          |

|           |      | 6.3.1 Cosmetic Check (Display Off) in Non-Active Area           | 16          |

|           |      | 6.3.2 Cosmetic Check (Display Off) in Active Area               | 18          |

|           |      | 6.3.3 Pattern Check (Display On) in Active Area                 | 19          |

| <i>7.</i> | Pac  | ckage Specifications                                            | 20          |

| <i>8.</i> | Pre  | ecautions When Using These OEL Display Modules21                | ~ <i>23</i> |

|           | 8.1  | Handling Precautions                                            | 21          |

|           | 8.2  | Storage Precautions                                             | 21          |

|           | 8.3  | Designing Precautions                                           | 22          |

|           | 8.4  | Precautions when disposing of the OEL display modules           | 22          |

|           | 8.5  | Other Precautions                                               | 22          |

| W         | arra | anty                                                            | 23          |

| No        | tice | e                                                               | 23          |

# 1. Basic Specifications

#### 1.1 Display Specifications

1) Display Mode: Passive Matrix

2) Display Color: Monochrome with 16 Gray Scales (Light Blue)

3) Drive Duty: 1/64 Duty

# 1.2 Mechanical Specifications

Outline Drawing: According to the annexed outline drawing

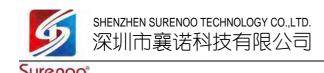

2) Number of Pixels:  $256 \times 64$

3) Module Size:  $84.00 \times 45.80 \times 2.00$  (mm)

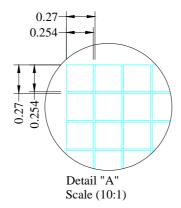

4) Panel Size:  $84.00 \times 25.80 \times 2.00$  (mm) including "Glare Polarizer"

5) Active Area:  $69.104 \times 17.264 \text{ (mm)}$ 6) Pixel Pitch:  $0.27 \times 0.27 \text{ (mm)}$ 7) Pixel Size:  $0.254 \times 0.254 \text{ (mm)}$ 8) Weight:  $8.80 \text{ (g)} \pm 10\%$

#### 1.3 Active Area / Memory Mapping & Pixel Construction

www.surenoo.com - 03 -

- 40

# 1.4 Mechanical Drawing

# 1.5 Pin Definition

| Pin Number   | Symbol        | I/O | Function                                                                                                                                                                                                                                                                                                                                  |  |  |

|--------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Power Suppl  | 'y            |     |                                                                                                                                                                                                                                                                                                                                           |  |  |

| 26           | VCI           | Р   | Power Supply for Operation  This is a voltage supply pin. It must be connected to external source & always be equal to or higher than $V_{DD}$ & $V_{DDIO}$ .                                                                                                                                                                             |  |  |

| 25           | VDD           | Р   | Power Supply for Core Logic Circuit  This is a voltage supply pin. It can be supplied externally (within the range of 2.4~2.6V) or regulated internally from V <sub>CI</sub> . A capacitor should be connected between this pin & V <sub>SS</sub> under all circumstances.                                                                |  |  |

| 24           | VDDIO         | Р   | Power Supply for I/O Pin  This pin is a power supply pin of I/O buffer. It should be connected to $V_{CI}$ external source. All I/O signal should have $V_{IH}$ reference to $V_{DDIO}$ . When I signal pins (BS0~BS1, D0~D7, control signals) pull high, they should connected to $V_{DDIO}$ .                                           |  |  |

| 2            | VSS           | Р   | Ground of Logic Circuit  This is a ground pin. It also acts as a reference for the logic pins. It must be connected to external ground.                                                                                                                                                                                                   |  |  |

| 3, 29        | VCC           | Р   | Power Supply for OEL Panel  These are the most positive voltage supply pin of the chip. They must be connected to external source.                                                                                                                                                                                                        |  |  |

| 5, 28        | VLSS          | Р   | <b>Ground of Analog Circuit</b> These are the analog ground pins. They should be connected to V <sub>SS</sub> external                                                                                                                                                                                                                    |  |  |

| Driver       |               |     |                                                                                                                                                                                                                                                                                                                                           |  |  |

| 22           | IREF<br>VCOMH | I   | Current Reference for Brightness Adjustment  This pin is segment current reference pin. A resistor should be connected between this pin and V <sub>ss</sub> . Set the current at 10µA maximum.  Voltage Output High Level for COM Signal                                                                                                  |  |  |

| 4            | VCOIVIII      |     | This pin is the input pin for the voltage output high level for COM signals. A tantalum capacitor should be connected between this pin and V <sub>ss</sub> .                                                                                                                                                                              |  |  |

| 27           | VSL           | Р   | $\begin{tabular}{lll} \textbf{Voltage Output Low Level for SEG Signal} \\ This is segment voltage reference pin. \\ When external $V_{SL}$ is not used, this pin should be left open. \\ When external $V_{SL}$ is used, this pin should connect with resistor and diode to ground. \\ \end{tabular}$                                     |  |  |

| Testing Pads | •             |     |                                                                                                                                                                                                                                                                                                                                           |  |  |

| 21           | FR            | 0   | Frame Frequency Triggering Signal  This pin will send out a signal that could be used to identify the driver status.  Nothing should be connected to this pin. It should be left open individually.                                                                                                                                       |  |  |

| Interface    |               |     |                                                                                                                                                                                                                                                                                                                                           |  |  |

| 16<br>17     | BS0<br>BS1    | I   | Communicating Protocol Select These pins are MCU interface selection input. See the following table:    BS0 BS1     3-wire Serial   1 0     4-wire Serial   0 0     8-bit 68XX Parallel   1 1     8-bit 80XX Parallel   0 1                                                                                                               |  |  |

| 20           | RES#          | I   | Power Reset for Controller and Driver  This pin is reset signal input. When the pin is low, initialization of the chip is executed. Keep this pin pull high during normal operation.                                                                                                                                                      |  |  |

| 19           | CS#           | I   | Chip Select This pin is the chip select input. The chip is enabled for MCU communication only when CS# is pulled low.                                                                                                                                                                                                                     |  |  |

| 18           | D/C#          | I   | Data/Command Control This pin is Data/Command control pin. When the pin is pulled high, the input at D7~D0 is treated as display data. When the pin is pulled low, the input at D7~D0 will be transferred to the command register. For detail relationship to MCU interface signals, please refer to the Timing Characteristics Diagrams. |  |  |

www.surenoo.com - 05 -

# 1.5 Pin Definition (Continued)

| Pin Number    | Symbol    | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface (Co | ontinued) |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14            | E/RD#     | I   | Read/Write Enable or Read  This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as the Enable (E) signal. Read/write operation is initiated when this pin is pulled high and the CS# is pulled low.  When connecting to an 80XX-microprocessor, this pin receives the Read (RD#) signal. Data read operation is initiated when this pin is pulled low and CS# is pulled low.  When serial mode is selected, this pin must be connected to Vss. |

| 15            | R/W#      | I   | Read/Write Select or Write  This pin is MCU interface input. When interfacing to a 68XX-series microprocessor, this pin will be used as Read/Write (R/W#) selection input. Pull this pin to "High" for read mode and pull it to "Low" for write mode.  When 80XX interface mode is selected, this pin will be the Write (WR#) input. Data write operation is initiated when this pin is pulled low and the CS# is pulled low.  When serial mode is selected, this pin must be connected to Vss.    |

| 6~13          | D7~D0     | I/O | Host Data Input/Output Bus  These pins are 8-bit bi-directional data bus to be connected to the microprocessor's data bus. When serial mode is selected, D1 will be the serial data input SDIN and D0 will be the serial clock input SCLK.  Unused pins must be connected to V <sub>SS</sub> except for D2 in serial mode.                                                                                                                                                                         |

| Reserve       |           |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23            | N.C (GND) |     | Reserved Pin The N.C. pin between function pins is reserved for compatible and flexible design. Reserved Pin (Supporting Pin) The supporting pins can reduce the influences from stresses on the function pins. These pins must be connected to external ground as the ESD protection circuit.                                                                                                                                                                                                     |

www.surenoo.com - 06 -

# 1.6 Block Diagram

MCU Interface Selection: BS0 and BS1

Pins connected to MCU interface: D7~D0, E/RD#, R/W#, D/C#, CS#, and RES#

C1, C3, C5: 0.1µF C2, C4: 4.7µF C6: 10µF C7: 1µF

C8: 4.7µF / 25V Tantalum Capacitor

R1:  $680k\Omega$ , R1 = (Voltage at IREF - VSS) / IREF

R2: 50Ω, 1/4W D1:  $^{\circ}1.4V$ , 0.5W

www.surenoo.com - 07 -

# 2. Absolute Maximum Ratings

| Parameter                             | Symbol             | Min    | Max               | Unit | Notes |

|---------------------------------------|--------------------|--------|-------------------|------|-------|

| Supply Voltage for Operation          | $V_{CI}$           | -0.3   | 4                 | V    | 1, 2  |

| Supply Voltage for Logic              | $V_{DD}$           | -0.5   | 2.75              | V    | 1, 2  |

| Supply Voltage for I/O Pins           | $V_{	extsf{DDIO}}$ | -0.5   | $V_{\mathrm{CI}}$ | V    | 1, 2  |

| Supply Voltage for Display            | $V_{CC}$           | -0.5   | 16                | V    | 1, 2  |

| Operating Current for $V_{\text{CC}}$ | ${ m I}_{ m CC}$   | -      | 60                | mA   | 1, 2  |

| Operating Temperature                 | $T_OP$             | -40    | 85                | °C   | 3     |

| Storage Temperature                   | $T_{STG}$          | -40    | 90                | °C   | 3     |

| Life Time (80 cd/m²)                  |                    | 10,000 | -                 | hour | 4     |

| Life Time (60 cd/m²)                  |                    | 20,000 | -                 | hour | 4     |

Note 1: All the above voltages are on the basis of " $V_{SS} = 0V$ ".

Note 2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the module may occur. Also, for normal operations, it is desirable to use this module under the conditions according to Section 3. "Optics & Electrical Characteristics". If this module is used beyond these conditions, malfunctioning of the module can occur and the reliability of the module may deteriorate.

Note 3: The defined temperature ranges do not include the polarizer. The maximum withstood temperature of the polarizer should be 80°C.

Note 4:  $V_{cc} = 12.0V$ ,  $T_a = 25^{\circ}C$ , 50% Checkerboard.

Software configuration follows Section 4.4 Initialization.

End of lifetime is specified as 50% of initial brightness reached. The average operating lifetime at room temperature is estimated by the accelerated operation at high temperature conditions.

www.surenoo.com - 08 -

# 3. Optics & Electrical Characteristics

#### 3.1 Optics Characteristics

| Characteristics    | Symbol          | Conditions  | Min          | Тур          | Max          | Unit              |

|--------------------|-----------------|-------------|--------------|--------------|--------------|-------------------|

| Brightness         | L <sub>br</sub> | Note 5      | 60           | 80           | -            | cd/m <sup>2</sup> |

| C.I.E. (Blue)      | (x)<br>(y)      | C.I.E. 1931 | 0.12<br>0.22 | 0.16<br>0.26 | 0.20<br>0.30 |                   |

| Dark Room Contrast | CR              |             | _            | >10,000:1    | -            |                   |

| Viewing Angle      |                 |             | -            | Free         | -            | degree            |

<sup>\*</sup> Optical measurement taken at  $V_{CI} = 2.8V$ ,  $V_{CC} = 12.0V$ . Software configuration follows Section 4.4 Initialization.

#### 3.2 DC Characteristics

| Characteristics                                                   | Symbol                                   | Conditions            | Min                   | Тур  | Max                   | Unit |

|-------------------------------------------------------------------|------------------------------------------|-----------------------|-----------------------|------|-----------------------|------|

| Supply Voltage for Operation                                      | $V_{CI}$                                 |                       | 2.4                   | 2.8  | 3.5                   | V    |

| Supply Voltage for Logic                                          | $V_{DD}$                                 |                       | 2.4                   | 2.5  | 2.6                   | V    |

| Supply Voltage for I/O Pins                                       | V <sub>ppIO</sub>                        |                       | 1.65                  | 1.8  | V <sub>CI</sub>       |      |

| Supply Voltage for Display                                        | $V_{cc}$                                 | Note 5                | 11.5                  | 12   | 12.5                  |      |

| High Level Input                                                  | V <sub>IH</sub>                          |                       | $0.8 \times V_{DDIO}$ | -    | V <sub>DDIO</sub>     | V    |

| Low Level Input                                                   | $V_{IL}$                                 |                       | 0                     | -    | $0.2 \times V_{DDIO}$ | V    |

| High Level Output                                                 | $V_{OH}$                                 | $I_{out} = 100 \mu A$ | $0.9 \times V_{DDIO}$ | -    | $V_{\text{DDIO}}$     | V    |

| Low Level Output                                                  | $V_{OL}$                                 | $I_{out} = 100 \mu A$ | 0                     | -    | $0.1 \times V_{DDIO}$ | V    |

| Operating Current for $V_{\text{CI}}$                             | ${ m I}_{ m CI}$                         |                       | -                     | 180  | 300                   | μΑ   |

|                                                                   | _                                        | Note 6                |                       | 17.8 | 22.3                  | mA   |

| Operating Current for $V_{CC}$<br>Sleep Mode Current for $V_{CI}$ | ${ m I}_{ m CC}$ ${ m I}_{ m CI,~SLEEP}$ | Note 7                | -                     | 28.1 | 35.1                  | mA   |

| Siesp Head Surferie of Va                                         | -CI, SLEEP                               | Note 8                | -                     | 47.7 | 59.7                  | mA   |

| Sleep Mode Current for V <sub>CC</sub>                            | ${ m I}_{ m CC,~SLEEP}$                  |                       | -                     | 20   | 100                   | μΑ   |

| Sleep Mode Current for V <sub>CC</sub>                            | $I_{\text{CC, SLEEP}}$                   |                       | -                     | 2    | 10                    | μΑ   |

Note 5: Brightness  $(L_{br})$  and Supply Voltage for Display  $(V_{CC})$  are subject to the change of the panel characteristics and the customer's request.

www.surenoo.com - 09 -

Note 6:  $V_{CI}$  = 2.8V,  $V_{CC}$  = 12.0V, 30% Display Area Turn on.

Note 7:  $V_{CI}=2.8V$ ,  $V_{CC}=12.0V$ , 50% Display Area Turn on. Note 8:  $V_{CI}=2.8V$ ,  $V_{CC}=12.0V$ , 100% Display Area Turn on.

<sup>\*</sup> Software configuration follows Section 4.4 Initialization.

#### 3.3 AC Characteristics

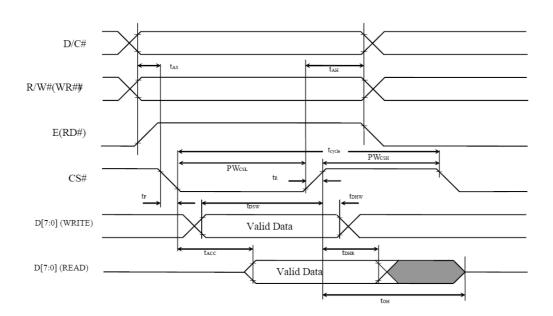

# 3.3.1 68XX-Series MPU Parallel Interface Timing Characteristics:

| Symbol                               | Description                                                                                                  | Min | Max      | Unit |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|----------|------|

| t <sub>cycle</sub>                   | Clock Cycle Time                                                                                             | 300 | -        | ns   |

| t <sub>AS</sub>                      | Address Setup Time                                                                                           | 10  | -        | ns   |

| t <sub>AH</sub>                      | Address Hold Time                                                                                            | 0   | -        | ns   |

| t <sub>DSW</sub>                     | Write Data Setup Time                                                                                        | 40  | -        | ns   |

| t <sub>DHW</sub>                     | Write Data Hold Time                                                                                         | 7   | -        | ns   |

| <b>t</b> <sub>DHR</sub>              | Read Data Hold Time                                                                                          | 20  | -        | ns   |

| t <sub>OH</sub>                      | Output Disable Time                                                                                          | _   | 70       | ns   |

| t <sub>ACC</sub>                     | Access Time                                                                                                  | _   | 140      | ns   |

| DW                                   | Chip Select Low Pulse Width (Read)                                                                           | 120 | <b>-</b> | ns   |

| $PW_{CSL}$                           | Chip Select Low Pulse Width (Write)                                                                          | 60  |          |      |

| D\A/                                 | Chip Select High Pulse Width (Read)                                                                          | 60  |          |      |

| PW <sub>CSH</sub>                    | Chip Select High Pulse Width (Write)                                                                         | 60  | _        | ns   |

| t <sub>R</sub>                       | Rise Time                                                                                                    | -   | 15       | ns   |

| t <sub>F</sub>                       | Fall Time                                                                                                    | -   | 15       | ns   |

| * (V <sub>DD</sub> - V <sub>SS</sub> | $= 2.4 \text{V}$ to 2.6V, $V_{DDIO} = 1.6 \text{V}$ , $V_{O} = 2.8 \text{V}$ , $T_{a} = 25 ^{\circ}\text{C}$ |     |          |      |

www.surenoo.com - 10 -

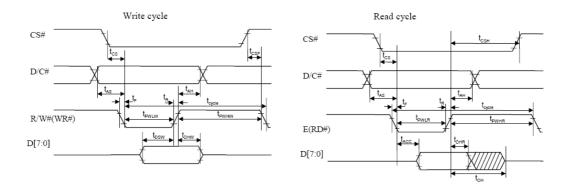

# 3.3.2 80XX-Series MPU Parallel Interface Timing Characteristics:

| Symbol             | Description                          | Min | Max  | Unit |

|--------------------|--------------------------------------|-----|------|------|

| t <sub>cycle</sub> | Clock Cycle Time                     | 300 | -    | ns   |

| t <sub>AS</sub>    | Address Setup Time                   | 10  | -    | ns   |

| t <sub>AH</sub>    | Address Hold Time                    | 0   | -    | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time                | 40  | -    | ns   |

| $t_DHW$            | Write Data Hold Time                 | 7   | -    | ns   |

| $t_{DHR}$          | Read Data Hold Time                  | 20  | -    | ns   |

| t <sub>OH</sub>    | Output Disable Time                  | -   | 70   | ns   |

| t <sub>ACC</sub>   | Access Time                          | -   | 140  | ns   |

| t <sub>PWLR</sub>  | Read Low Time                        | 150 | -    | ns   |

| t <sub>PWLW</sub>  | Write Low Time                       | 60  | -    | ns   |

| t <sub>PWHR</sub>  | Read High Time                       | 60  | -    | ns   |

| t <sub>PWHW</sub>  | Write High Time                      | 60  | -    | ns   |

| t <sub>CS</sub>    | Chip Select Setup Time               | 0   | -    | ns   |

| tçsh               | Chip Select Hold Time to Read Signal | 0   |      | ns   |

| t <sub>CSF</sub>   | Chip Select Hold Time                | 20  |      | ns   |

| t <sub>R</sub>     | Rise Time                            | -   | //15 | ns.  |

| t <sub>F</sub>     | Fall Time                            | -   | 15   | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 2.4V \text{ to } 2.6V, V_{DDIO} = 1.6V, V_{CI} = 2.8V, T_a = 25^{\circ}C)$

www.surenoo.com - 11 -

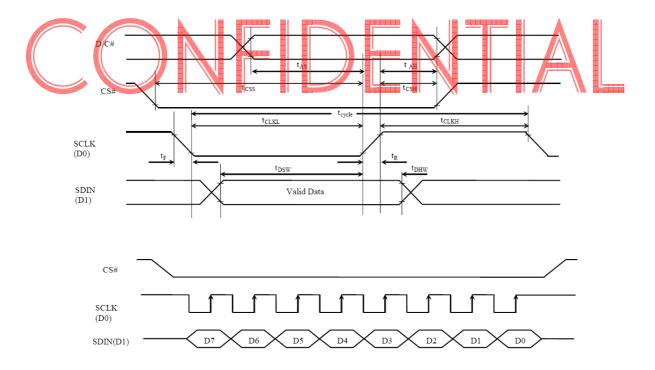

# 3.3.3 Serial Interface Timing Characteristics: (4-wire Serial)

| Symbol            | Description            | Min | Max | Unit |

|-------------------|------------------------|-----|-----|------|

| $t_{cycle}$       | Clock Cycle Time       | 100 | -   | ns   |

| t <sub>AS</sub>   | Address Setup Time     | 15  | -   | ns   |

| t <sub>AH</sub>   | Address Hold Time      | 15  | -   | ns   |

| $t_{CSS}$         | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>  | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>  | Write Data Setup Time  | 15  | -   | ns   |

| $t_{DHW}$         | Write Data Hold Time   | 15  | -   | ns   |

| t <sub>CLKL</sub> | Clock Low Time         | 20  | -   | ns   |

| t <sub>CLKH</sub> | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>    | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>    | Fall Time              | -   | 15  | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 2.4V \text{ to } 2.6V, V_{DDIO} = 1.6V, V_{CI} = 2.8V, T_a = 25^{\circ}C)$

www.surenoo.com - 12 -

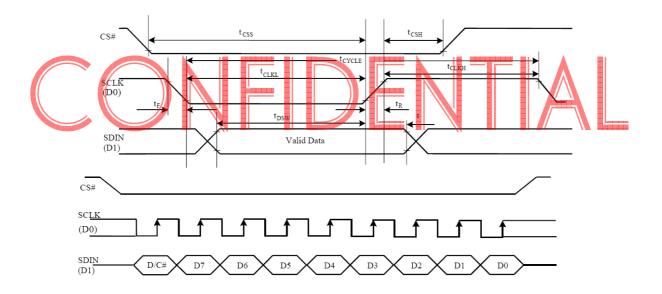

# 3.3.4 Serial Interface Timing Characteristics: (3-wire Serial)

| Symbol             | Description            | Min | Max | Unit |

|--------------------|------------------------|-----|-----|------|

| t <sub>cycle</sub> | Clock Cycle Time       | 100 | -   | ns   |

| t <sub>CSS</sub>   | Chip Select Setup Time | 20  | -   | ns   |

| t <sub>CSH</sub>   | Chip Select Hold Time  | 10  | -   | ns   |

| t <sub>DSW</sub>   | Write Data Setup Time  | 15  | -   | ns   |

| t <sub>DHW</sub>   | Write Data Hold Time   | 15  | -   | ns   |

| t <sub>CLKL</sub>  | Clock Low Time         | 20  | -   | ns   |

| t <sub>CLKH</sub>  | Clock High Time        | 20  | -   | ns   |

| t <sub>R</sub>     | Rise Time              | -   | 15  | ns   |

| t <sub>F</sub>     | Fall Time              | -   | 15  | ns   |

<sup>\*</sup>  $(V_{DD} - V_{SS} = 2.4V \text{ to } 2.6V, V_{DDIO} = 1.6V, V_{CI} = 2.8V, T_a = 25^{\circ}C)$

www.surenoo.com - 13 -

# 4. Functional Specification

#### 4.1 Commands

Refer to the Technical Manual for the SSD1322

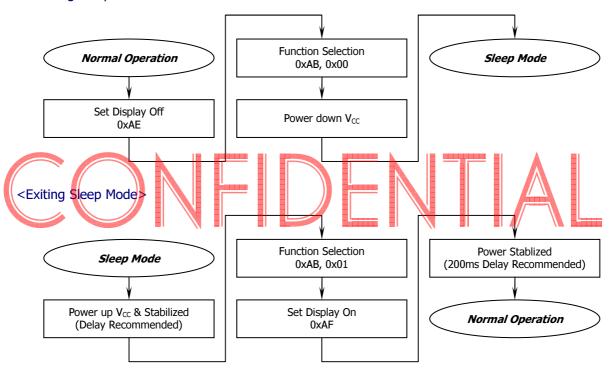

#### 4.2 Power down and Power up Sequence

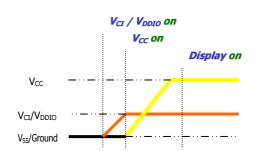

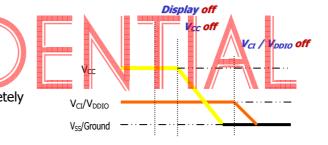

To protect OEL panel and extend the panel life time, the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. It gives the OEL panel enough time to complete the action of charge and discharge before/after the operation.

#### 4.2.1 Power up Sequence:

- 1. Power up  $V_{CI} / V_{DDIO}$

- 2. Send Display off command

- 3. Initialization

- 4. Clear Screen

- 5. Power up V<sub>CC</sub>

- 6. Delay 200ms (When V<sub>CC</sub> is stable)

- 7. Send Display on command

- 1. Send Display off command

- 2. Power down V

- When V<sub>CC</sub> is reach 0 and panel is completely discharges)

- 4. Power down  $V_{CI}$  /  $V_{DDIO}$

#### Note 9:

- 1) Since an ESD protection circuit is connected between  $V_{CI}$ ,  $V_{DDIO}$  and  $V_{CC}$  inside the driver IC,  $V_{CC}$  becomes lower than  $V_{CI}$  whenever  $V_{DD}$ ,  $V_{DDIO}$  is ON and  $V_{CC}$  is OFF.

- 2) V<sub>CC</sub> should be kept float (disable) when it is OFF.

- 3) Power Pins ( $V_{DD}$ ,  $V_{DDIO}$ ,  $V_{CC}$ ) can never be pulled to ground under any circumstance.

- 4)  $V_{CL}$ ,  $V_{DDIO}$  should not be power down before  $V_{CC}$  power down.

#### 4.3 Reset Circuit

When RES# input is low, the chip is initialized with the following status:

- 1. Display is OFF

- 2. 480×128 Display Mode

- 3. Normal segment and display data column and row address mapping (SEG0 mapped to column address 00h and COM0 mapped to row address 00h)

- 4. Display start line is set at display RAM address 0

- 5. Column address counter is set at 0

- 6. Normal scan direction of the COM outputs

- 7. Contrast control register is set at 7Fh

www.surenoo.com - 14 -

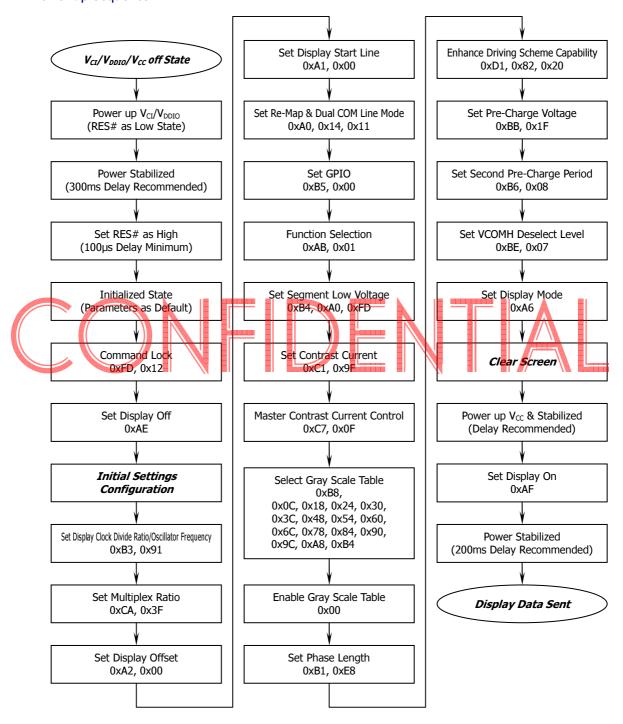

#### 4.4 Actual Application Example

Command usage and explanation of an actual example

#### <Power up Sequence>

If the noise is accidentally occurred at the displaying window during the operation, please reset the display in order to recover the display function.

www.surenoo.com - 15 -

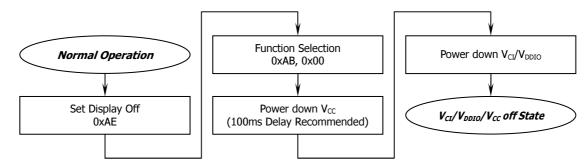

# <Power down Sequence>

# <Entering Sleep Mode>

www.surenoo.com - 16 -

表 6 件权 月晚公司 Model No.: SOG25664C\_P280

# 5. Reliability

# **5.1 Contents of Reliability Tests**

| Item                                | Conditions                                | Criteria        |

|-------------------------------------|-------------------------------------------|-----------------|

| High Temperature Operation          | 85°C, 500 hrs                             |                 |

| Low Temperature Operation           | -40°C, 500 hrs                            |                 |

| High Temperature Storage            | 90°C, 500 hrs                             | The operational |

| Low Temperature Storage             | -40°C, 500 hrs                            | functions work. |

| High Temperature/Humidity Operation | 60°C, 90% RH, 240 hrs                     |                 |

| Thermal Shock                       | -40°C ⇔ 85°C, 100 cycles<br>30 mins dwell | -               |

<sup>\*</sup> The samples used for the above tests do not include polarizer.

#### **5.2 Failure Check Standard**

After the completion of the described reliability test, the samples were left at room temperature for 2 hrs prior to conducting the failure test at  $23\pm5^{\circ}$ C;  $55\pm15\%$  RH.

www.surenoo.com - 17 -

<sup>\*</sup> No moisture condensation is observed during tests.

# 6. Outgoing Quality Control Specifications

#### **6.1 Environment Required**

Customer's test & measurement are required to be conducted under the following conditions:

Temperature:  $23 \pm 5^{\circ}\text{C}$  Humidity:  $55 \pm 15\% \text{ RH}$

Fluorescent Lamp: 30W Distance between the Panel & Lamp:  $\geq$  50cm Distance between the Panel & Eyes of the Inspector:  $\geq$  30cm Finger glove (or finger cover) must be worn by the inspector.

Inspection table or jig must be anti-electrostatic.

#### 6.2 Sampling Plan

Level II, Normal Inspection, Single Sampling, MIL-STD-105E

# 6.3 Criteria & Acceptable Quality Level

| Partition      | AQL              | Definition                              |  |

|----------------|------------------|-----------------------------------------|--|

| Major          | 0.65             | Defects in Pattern Check (Display On)   |  |

| Minor          | 1.0              | Defects in Cosmetic Check (Display Off) |  |

| 6.3.1 Cosmetic | Check (Display ( | Off) in Non-Active Area                 |  |

| Check Item             | Classification | Criteria                                                    |

|------------------------|----------------|-------------------------------------------------------------|

| Panel General Chipping | Minor          | X > 6 mm (Along with Edge) Y > 1 mm (Perpendicular to edge) |

www.surenoo.com - 18 -

6.3.1 Cosmetic Check (Display Off) in Non-Active Area (Continued)

| Check Item                                                       | Classification | Criteria                              |

|------------------------------------------------------------------|----------------|---------------------------------------|

| Panel Crack                                                      | Minor          | Any crack is not allowable.           |

| Copper Exposed<br>(Even Pin or Film)                             | Minor          | Not Allowable by Naked Eye Inspection |

| Film or Trace Damage  Terminal Lead Prober Mark                  | Minor          |                                       |

| Glue or Contamination on Pin<br>(Couldn't Be Removed by Alcohol) | Minor          |                                       |

| Ink Marking on Back Side of panel (Exclude on Film)              | Acceptable     | Ignore for Any                        |

*www.surenoo.com* - 19 -

# 6.3.2 Cosmetic Check (Display Off) in Active Area

It is recommended to execute in clear room environment (class 10k) if actual in necessary.

| Check Item                                                       | Classification | Criteria                                                                    |

|------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------|

| Any Dirt & Scratch on Polarizer's Protective Film                | Acceptable     | Ignore for not Affect the Polarizer                                         |

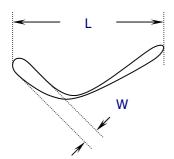

| Scratches, Fiber, Line-Shape Defect<br>(On Polarizer)            | Minor          | $W \le 0.1$ Ignore $W > 0.1$ $L \le 2$ $n \le 1$ $L > 2$ $n = 0$            |

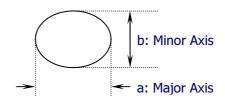

| Dirt, Black Spot, Foreign Material,<br>(On Polarizer)            | Minor          | $\Phi \le 0.1$ Ignore $0.1 < \Phi \le 0.25$ $n \le 1$ $0.25 < \Phi$ $n = 0$ |

| Dent, Bubbles, White spot<br>(Any Transparent Spot on Polarizer) | Minor          | $\Phi \le 0.5$ → Ignore if no Influence on Display $0.5 < \Phi$ $n = 0$     |

| Fingerprint, Flow Mark (On Polarizer)                            | Minor          | Not Allowable                                                               |

Protective film should not be tear off when cosmetic check.

<sup>\*\*</sup> Definition of W & L &  $\Phi$  (Unit: mm):  $\Phi$  = (a + b) / 2

www.surenoo.com - 20 -

# 6.3.3 Pattern Check (Display On) in Active Area

|  | Check Item    | Classification | Criteria |

|--|---------------|----------------|----------|

|  | No Display    | Major          |          |

|  | Missing Line  | Major          |          |

|  | Rixel Short   | Major          |          |

|  | Darker Pixel  | Major          |          |

|  | Wrong Display | Major          |          |

|  | Un-uniform    | Major          |          |

*www.surenoo.com* - 21 -

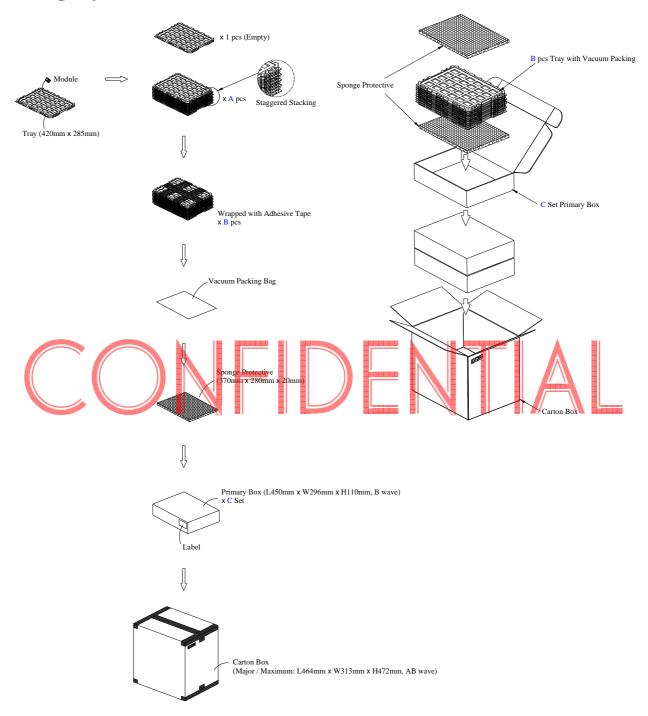

# 7. Package Specifications

| Item          |     | Quantity |                                          |

|---------------|-----|----------|------------------------------------------|

| Module        |     | 210      | per Primary Box                          |

| Holding Trays | (A) | 15       | per Primary Box                          |

| Total Trays   | (B) | 16       | per Primary Box (Including 1 Empty Tray) |

| Primary Box   | (C) | 1~4      | per Carton (4 as Major / Maximum)        |

www.surenoo.com - 22 -

# 8. Precautions When Using These OEL Display Modules

#### 8.1 Handling Precautions

1) Since the display panel is being made of glass, do not apply mechanical impacts such us dropping from a high position.

Model No.: SOG25664C P280

- 2) If the display panel is broken by some accident and the internal organic substance leaks out, be careful not to inhale nor lick the organic substance.

- 3) If pressure is applied to the display surface or its neighborhood of the OEL display module, the cell structure may be damaged and be careful not to apply pressure to these sections.

- 4) The polarizer covering the surface of the OEL display module is soft and easily scratched. Please be careful when handling the OEL display module.

- 5) When the surface of the polarizer of the OEL display module has soil, clean the surface. It takes advantage of by using following adhesion tape.

- \* Scotch Mending Tape No. 810 or an equivalent

- Never try to breathe upon the soiled surface nor wipe the surface using cloth containing solvent such as ethyl alcohol, since the surface of the polarizer will become cloudy.

Also, pay attention that the following liquid and solvent may spoil the polarizer:

- \* Water

- \* Ketone

- \* Aromatic Solvents

- 6) Hold OEL display module very carefully when placing OEL display module into the system housing. Do not apply excessive stress or pressure to OEL display module. And, do not over bend the film with electrode pattern layouts. These stresses will influence the display performance. Also, secure sufficient rigidity for the outer cases.

- 7) Do not apply stress to the driver IC and the surrounding molded sections.

- 8) Do not disassemble nor modify the OEL display module.

- 9) Do not apply input signals while the logic power is off.

- 10) Pay sufficient attention to the working environments when handing OEL display modules to prevent occurrence of element breakage accidents by static electricity.

- \* Be sure to make human body grounding when handling OEL display modules.

- \* Be sure to ground tools to use or assembly such as soldering irons.

- \* To suppress generation of static electricity, avoid carrying out assembly work under dry environments.

- \* Protective film is being applied to the surface of the display panel of the OEL display module. Be careful since static electricity may be generated when exfoliating the protective film.

- 11) Protection film is being applied to the surface of the display panel and removes the protection film before assembling it. At this time, if the OEL display module has been stored for a long period of time, residue adhesive material of the protection film may remain on the surface of the display panel after removed of the film. In such case, remove the residue material by the method introduced in the above Section 5).

- 12) If electric current is applied when the OEL display module is being dewed or when it is placed under high humidity environments, the electrodes may be corroded and be careful to avoid the above.

#### 8.2 Storage Precautions

1) When storing OEL display modules, put them in static electricity preventive bags avoiding exposure to direct sun light nor to lights of fluorescent lamps. and, also, avoiding high temperature and high

www.surenoo.com - 23 -

Model No.: SOG25664C P280

humidity environment or low temperature (less than  $0^{\circ}$ C) environments. (We recommend you to store these modules in the packaged state when they were shipped from WiseChip Semiconductor Inc.)

At that time, be careful not to let water drops adhere to the packages or bags nor let dewing occur with them.

2) If electric current is applied when water drops are adhering to the surface of the OEL display module, when the OEL display module is being dewed or when it is placed under high humidity environments, the electrodes may be corroded and be careful about the above.

#### 8.3 Designing Precautions

- 1) The absolute maximum ratings are the ratings which cannot be exceeded for OEL display module, and if these values are exceeded, panel damage may be happen.

- 2) To prevent occurrence of malfunctioning by noise, pay attention to satisfy the  $V_{IL}$  and  $V_{IH}$  specifications and, at the same time, to make the signal line cable as short as possible.

- 3) We recommend you to install excess current preventive unit (fuses, etc.) to the power circuit ( $V_{CI}$ ). (Recommend value: 0.5A)

- 4) Pay sufficient attention to avoid occurrence of mutual noise interference with the neighboring devices.

- 5) As for EMI, take necessary measures on the equipment side basically.

- 6) When fastening the OEL display module, fasten the external plastic housing section.

- 7) If power supply to the OEL display module is forcibly shut down by such errors as taking out the main battery while the OEL display panel is in operation, we cannot guarantee the quality of this OEL display module.

- 8) The electric potential to be connected to the rear face of the IC chip should be as follows: SSD1322

\* Connection (contact) to any other potential than the above may lead to rupture of the IC.

#### 8.4 Precautions when disposing of the OEL display modules

1) Request the qualified companies to handle industrial wastes when disposing of the OEL display modules. Or, when burning them, be sure to observe the environmental and hygienic laws and regulations.

#### 8.5 Other Precautions

- 1) When an OEL display module is operated for a long of time with fixed pattern may remain as an after image or slight contrast deviation may occur.

- Nonetheless, if the operation is interrupted and left unused for a while, normal state can be restored. Also, there will be no problem in the reliability of the module.

- 2) To protect OEL display modules from performance drops by static electricity rapture, etc., do not touch the following sections whenever possible while handling the OEL display modules.

- \* Pins and electrodes

- \* Pattern layouts such as the COF

- 3) With this OEL display module, the OEL driver is being exposed. Generally speaking, semiconductor elements change their characteristics when light is radiated according to the principle of the solar battery. Consequently, if this OEL driver is exposed to light, malfunctioning may occur.

- \* Design the product and installation method so that the OEL driver may be shielded from light in actual usage.

- \* Design the product and installation method so that the OEL driver may be shielded from light during the inspection processes.

- 4) Although this OEL display module stores the operation state data by the commands and the indication data, when excessive external noise, etc. enters into the module, the internal status may be changed. It therefore is necessary to take appropriate measures to suppress noise generation or to protect from influences of noise on the system design.

- 5) We recommend you to construct its software to make periodical refreshment of the operation

www.surenoo.com - 24 -

statuses (re-setting of the commands and re-transference of the display data) to cope with catastrophic noise.

Model No.: SOG25664C P280

#### Warranty:

The warranty period shall last twelve (12) months from the date of delivery. Buyer shall be completed to assemble all the processes within the effective twelve (12) months. WiseChip Semiconductor Inc. shall be liable for replacing any products which contain defective material or process which do not conform to the product specification, applicable drawings and specifications during the warranty period. All products must be preserved, handled and appearance to permit efficient handling during warranty period. The warranty coverage would be exclusive while the returned goods are out of the terms above.

#### Notice:

No part of this material may be reproduces or duplicated in any form or by any means without the written permission of WiseChip Semiconductor Inc. WiseChip Semiconductor Inc. reserves the right to make changes to this material without notice. WiseChip Semiconductor Inc. does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of Foreign Exchange and Foreign Trade Law of Taiwan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

#### © WiseChip Semiconductor Inc. 2011, All rights reserved.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

www.surenoo.com - 25 -